|

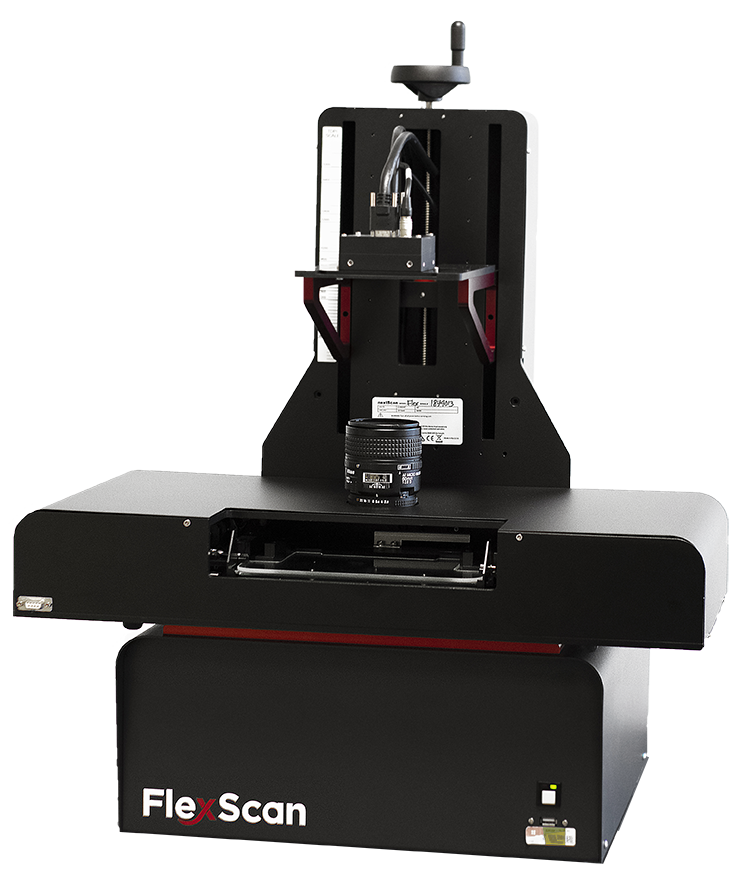

The Rx input pin will be ignored and the Tx output pin always to the recessive state (means logic 1). The bit stream output of the transmitter is internally fed back to the receiver input. Loop-Back mode, in this mode, FlexCAN performs an internal loop back that can be used for self-test operation.All memory-mapped register are configurable, except the PE submodule clock source select bit CTRL1. Freeze mode, in this mode, no transmission or reception of frames is done and synchronicity to the CAN bus is lost.It can be further divided into user mode and supervisor mode, which differ in the access to some restricted control registers. Normal mode, operates receiving and/or transmitting message frames, errors are managed normally, and all CAN Protocol functions are enabled.Compliant with the ISO 11898-1 standard.

Support for Flexible Data Rate (CAN FD) protocol specification and CAN 2.0 B protocol specifications.

The FlexCAN module can be divided into several submodules : The "Protocol Engine" (PE) submodule, The "Controller Host Interface" (CHI) submodule and The "Bus The FlexCAN module is a full implementation of the CAN protocol specification, the CAN with Flexible Data rate (CAN FD) protocol, and the CAN 2.0 version B protocol, which supports both standard and extended message frames and long payloads up to 64 bytes, transferred at faster rates (up to 8 Mbps). Peripheral feature and how this peripheral works

0 Comments

Leave a Reply. |

AuthorWrite something about yourself. No need to be fancy, just an overview. ArchivesCategories |

RSS Feed

RSS Feed